SC-M-71 0896 February 1972

CIRCUIT ANALYSIS USING THE DRIVING-POINT-IMPEDANCE TECHNIQUE

Thomas A. Howard Advanced Instrumentation Development Division

Issued by Sandia Corporation, A prime contractor to the United States Atomic Energy Commission

## **NOTICE**

This report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Atomic Energy Commission, nor any of their employees, nor any of their contractors, subcontractors, or their employees makes any warranty, express of implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights.

## SC-M-71 0896

# CIRCUIT ANALYSIS USING THE DRIVING-POINT-IMPEDANCE TECHNIQUE

Thomas A. Howard Advanced Instrumentation Development Division Sandia Laboratories, Albuquerque, New Mexico 87115

Printed - February 1972

## **Abstract**

This report presents a useful electronic circuit analysis and design technique which was developed at the University of New Mexico by Dr. R. D. Kelly.

## Acknowledgment

The technique presented in this paper was developed by Dr. R. D. Kelly, Professor of Electrical Engineering at the University of New Mexico. The author wishes to thank Dr. Kelly for his permission to present this material.

The blank pages in this report have been included to provide space for making notes. The report should be placed in a loose leaf notebook for most effective use.

## Contents

|                                                                                                             | Page |

|-------------------------------------------------------------------------------------------------------------|------|

| Introduction                                                                                                | 4    |

| Development of Voltage Divider Equations                                                                    | 5    |

| Development of Current Divider Equations                                                                    | 8    |

| Superposition Theorem                                                                                       | 14   |

| Driving-Point-Impedance (DPI) Equations                                                                     | 21   |

| Bipolar Transistor DPI Equations                                                                            | 21   |

| Triode/Pentode Vacuum Tube DPI Equations                                                                    | 24   |

| J-FET DPI Equations                                                                                         | 27   |

| Application of DPI Analysis to Some Simple Transistor Circuits                                              | 30   |

| Series Parallel Networks                                                                                    | 30   |

| Nonseries Parallel Networks                                                                                 | 38   |

| Application of DPI Analysis to a Feedback Amplifier                                                         | 43   |

| Appendix A - Review of Thevenin's and Norton's Theorems                                                     | 48   |

| Appendix B - Determination of Signal Current Directions in Active Devices Operating in Their Linear Regions | 53   |

| Appendix C - DPI Analysis and the Laplace Transform                                                         | 57   |

| Appendix D - Additional Examples of the Application of DPI Analysis                                         | 61   |

| References                                                                                                  | 71   |

## CIRCUIT ANALYSIS USING THE DRIVING-POINT-IMPEDANCE TECHNIQUE

## Introduction

This report presents a useful electronic circuit analysis and design technique which was developed at the University of New Mexico by Dr. R. D. Kelly, Professor of Electrical Engineering. It was written to satisfy the requests made by those Sandia Laboratories personnel who have been informally introduced to this technique and who have expressed the desire for a document of this type. It is the opinion of the author that this technique, known as Driving-Point-Impedance (DPI) Analysis, provides a far greater insight into electronic circuit operation than the more conventional loop, node, or signal flow graph analysis techniques. Once mastered, DPI analysis can be applied to a wide variety of electronic circuits, and quite frequently solutions to circuit problems can be written by inspection in a single step. Successful mastery of this technique requires a thorough knowledge of a few basic circuit theorems and manipulation of a simple set of useful equations for each active device considered, i.e., bipolar transistors, FET's, and vacuum tubes. In general, DPI analysis does not require that a circuit be redrawn with the active devices replaced by their linear models. Anyone who has taken a course in basic transistor circuit analysis is aware of the myriad number of equivalent circuits presented in such a course. The standard approach uses the various hybrid equivalent circuits, i.e., hybrid common emitter, common collector, and common base models, to obtain the desired circuit solutions. In addition to utilizing different transistor models in the analysis, it is quite common to make many simplifying assumptions beyond those already made for the active device models. Quite frequently, the end result of this approach is confusion on the part of the student. It is not uncommon to find circuit designers applying simplified transfer function equations to circuit designs while ignoring many of the original assumptions made during the derivation of these equations; naturally, the predicted circuit response may differ significantly from the actual response. In addition, the use of many different active device models involves many different parameters, some of which are certain to be missing from data sheets. The DPI approach simplifies the writing of transfer functions and requires only a single active device model for all transistor circuits.

Efficient application of DPI analysis to the solution of electronic circuits dictates that the writing of current and voltage divider equations, along with use of the Superposition Theorem, become almost automatic processes. Because of its importance, this material will be covered in the main body of the report, although individuals familiar with these basic concepts may desire to omit it. In order to keep the mathematics from obscuring the analysis technique, circuit solutions have been limited to do or the sinusoidal steady state. Those familiar with the application of the Laplace transform method can use it along with DPI analysis to solve transient circuit problems;

examples are given in Appendix C. Generally, all-resistive-type networks will be analyzed in order to demonstrate the desired points; however, DPI analysis can be utilized for other types of networks.

## Development of Voltage Divider Equations

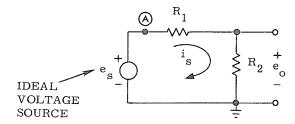

Figure 1 illustrates a simple two-resistor voltage divider.

Figure 1. Simple Resistive Voltage Divider

Using Ohm's Law to solve for  ${\tt e}_{\tt o}$  in terms of  ${\tt e}_{\tt s},~{\tt R}_{\tt 1}$  and  ${\tt R}_{\tt 2},~{\tt we}$  have

$$e_{o} = i_{s}R_{2}, \qquad (1)$$

$$i_s = \frac{e_s}{R_1 + R_2} \quad . \tag{2}$$

Substituting Equation (2) into (1), we have

$$e_{o} = e_{s} \left( \frac{R_{2}}{R_{1} + R_{2}} \right)$$

(3)

Equation (3) is referred to as a voltage divider equation. It should be clear that Equation (3) can be written in a single step once the pattern is recognized. Likewise, the voltage drop across  $R_1$  using point A as the positive reference terminal is

$$e_{R_1} = e_s \left( \frac{R_1}{R_1 + R_2} \right)$$

.

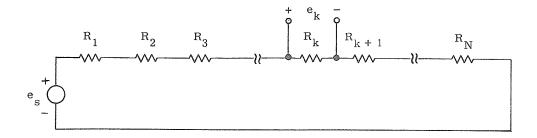

Figure 2 shows a generalized voltage divider circuit along with the voltage divider equation for the voltage drop across resistor  $R_{\mathbf{k}}$ .

$$e_{k} = e_{s} \left( \frac{R_{k}}{R_{1} + R_{2} + \dots + R_{N}} \right) = e_{s} \left( \frac{R_{k}}{\sum_{i=1}^{N} R_{i}} \right)$$

(4)

Figure 2. A Generalized Voltage Divider

Note especially that any of the  $\mathbf{R}_{\mathbf{i}}$  shown in Figure 2 may be a combination of other resistors. This point is demonstrated in the following example.

## Example 1

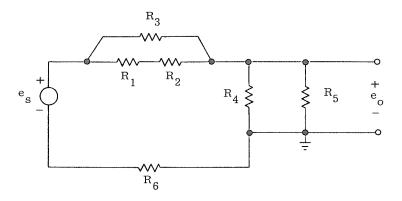

$\underline{\text{Problem}}\text{--Derive}$  an expression for  $e_0$  in terms of  $e_s$  and the resistors shown using the voltage divider equation (Equation 4).

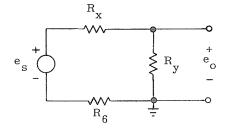

Solution -- We observe that this circuit can be reduced to the series combination of three resistors,

where  $R_x$  is  $R_3$  in parallel with the series combination of  $R_1$  and  $R_2$ , and  $R_y$  is the parallel combination of  $R_4$  and  $R_5$ . Using Equation (4), we have

$$e_{o} = e_{s} \left( \frac{R_{y}}{R_{x} + R_{y} + R_{6}} \right) , \qquad (5)$$

where

$$R_x = \frac{R_3(R_1 + R_2)}{R_3 + (R_1 + R_2)}$$

and  $R_y = \frac{R_4R_5}{R_4 + R_5}$ .

Substituting for  $\boldsymbol{R}_{\boldsymbol{x}}$  and  $\boldsymbol{R}_{\boldsymbol{y}}$  in Equation (5) yields

$$e_{o} = e_{s} \left[ \frac{\left(\frac{R_{4}R_{5}}{R_{4} + R_{5}}\right)}{\left(\frac{R_{3}[R_{1} + R_{2}]}{R_{3} + [R_{1} + R_{2}]}\right) + \left(\frac{R_{4}R_{5}}{R_{4} + R_{5}}\right) + R_{6}} \right]$$

(6)

Equations such as (6) can become cumbersome if more than a few resistors are contained in the network, so we introduce a shorthand notation for the parallel combination of two or more resistors. From this point on,  $R_i$  in parallel with  $R_i$  will be written as  $R_i \parallel R_i$  instead of

$$\frac{R_i R_j}{R_i + R_j}$$

and  $R = R_1 || R_2 || R_3 || \cdots || R_N$  will be interpreted to mean

$$R = \frac{1}{\frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3} + \cdots + \frac{1}{R_N}}$$

By using this notation for parallel resistors, one can write Equation (6) as

$$e_{o} = e_{s} \left[ \frac{(R_{4} || R_{5})}{(R_{4} || R_{5}) + (R_{3} || [R_{1} + R_{2}]) + R_{6}} \right].$$

(7)

Equation (7) has the form of a voltage divider equation and can be written in a single step directly from the original circuit diagram.

From this point on, all voltage divider equations will be written in the form of Equation (7).

## Example 2

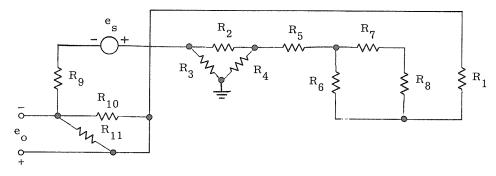

$\underline{\underline{\text{Problem}}}\text{--Using the following circuit, derive an expression for } e_{\text{O}} \text{ in a single step.} \quad \text{The expression must be in the form of a voltage divider equation.}$

Solution --

$$\mathbf{e_o} = \mathbf{e_s} \left[ \frac{ \left( \mathbf{R_{10} \mid \mid R_{11}} \right) }{ \left( \mathbf{R_{2} \mid \mid \lceil R_{3} + R_{4} \rceil} \right) + \mathbf{R_{5}} + \left( \mathbf{R_{6} \mid \mid \lceil R_{7} + R_{8} \rceil} \right) + \mathbf{R_{1}} + \left( \mathbf{R_{10} \mid \mid R_{11}} \right) + \mathbf{R_{9}} } \right] \cdot$$

## **Development of Current Divider Equations**

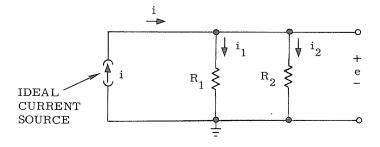

Figure 3 illustrates a simple two-resistor current divider.

Figure 3. Simple Current Divider

Using Ohm's Law to solve for  $i_1$ , we have

$$i_1 = \frac{e}{R_1} \quad (8)$$

and

$$e = i(R_1 \mid R_2) . (9)$$

Substituting Equation (9) into (8) and replacing  $\mathbf{R_1} || \mathbf{R_2}$  by  $\frac{\mathbf{R_1} \mathbf{R_2}}{\mathbf{R_1} + \mathbf{R_2}}$  , we have

$$i_1 = \frac{i(R_1||R_2)}{R_1} = \frac{i}{R_1} \left(\frac{R_1R_2}{R_1 + R_2}\right) = i\left(\frac{R_2}{R_1 + R_2}\right)$$

(10)

Equation (10) is referred to as a current divider equation. Equation (10) has a form similar to the voltage divider equation; but note that in the solution for  $i_1$ , which is the portion of i passing through  $R_1$ ,  $R_2$  is used in the divider fraction. Thus, the divider fraction uses the resistor opposite the one in which the current is to be determined. Figure 4 shows a generalized current divider circuit along with the equation for the current through resistor  $R_1$ .

$$i_{k} = i \left[ \frac{\left(R_{1} || R_{2} || R_{3} || \cdots || R_{k-1} || R_{k+1} || \cdots || R_{N}\right)}{\left(R_{1} || R_{2} || R_{3} || \cdots || R_{k-1} || R_{k+1} || \cdots || R_{N}\right) + R_{k}} \right]$$

(11)

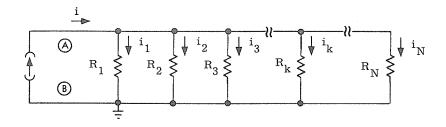

Figure 4. A Generalized Current Divider

Any of the  $R_i$  shown in Figure 4 can be a combination of other resistors which are connected between points  $\widehat{\mathbb{A}}$  and  $\widehat{\mathbb{B}}$ .

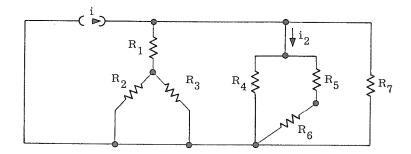

## Example 3

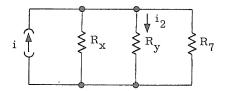

$\underline{\underline{Problem}}$ --Derive an expression for  $i_2$  in terms of i and the resistors shown and express the answer in the form of the current divider equation (Equation 11).

Solution -- We observe that this circuit can be reduced to the parallel combination of three resistors,

where  $R_x$  is  $R_1$  in series with the parallel combination of  $R_2$  and  $R_3$ , and  $R_y$  is  $R_4$  in parallel with the series combination of  $R_5$  and  $R_6$ .

Using Equation (11), we have

$$i_2 = i \left( \frac{\left[ R_x \middle| R_7 \right]}{\left[ R_x \middle| R_7 \right] + R_y} \right) \tag{12}$$

where

$$R_x = (R_1 + [R_2 | | R_3])$$

and  $R_y = (R_4 | | [R_5 + R_6])$

Substituting for  $\boldsymbol{R}_{\boldsymbol{x}}$  and  $\boldsymbol{R}_{\boldsymbol{y}}$  in Equation (12), we have

$$i_{2} = i \left[ \frac{\binom{R_{1} + \lceil R_{2} \rceil \rceil R_{3}}{\binom{R_{1} + \lceil R_{2} \rceil \rceil R_{3}}{\binom{R_{1} + \lceil R_{2} \rceil \rceil R_{3}} + \binom{R_{4} \rceil \lceil R_{5} + R_{6}}{\binom{R_{5} + R_{6}}}{\binom{R_{5} + R_{6}}{\binom{R_{5} + R_{6}}}{\binom{R_{5} + R_{6}}}{\binom{R_{5} + R_{6}}}}}}}}}}}}}} \right]}$$

Equation (13) can be written in a single step. The intermediate steps are included only to clarify the reasoning process.

#### Example 4

Solution --

$$i_{O} = i \left( \frac{\begin{bmatrix} R_1 + R_2 \end{bmatrix}}{\begin{bmatrix} R_1 + R_2 \end{bmatrix} + R_3} \right) . \tag{14}$$

The following examples will use voltage and current divider equations to obtain the desired solution. Additional steps will be included in order to demonstrate the reasoning process involved in obtaining the answer, but it is emphasized that the answer can and should be written in a single step. A facility for writing the answers in a single step must be gained in order to take full advantage of DPI analysis.

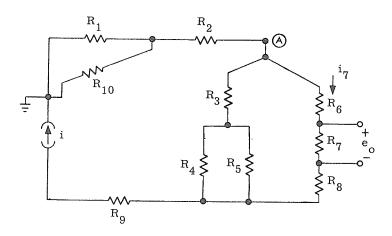

#### Example 5

$\underline{\text{Problem}}\text{--From the circuit below determine e}_{\text{O}}$  as a function of i and the resistors using current divider equations. Write the answer in a single step.

Solution -- Using a current divider equation and Ohm's Law, we obtain the solution

$$e_{o} = \underbrace{\left[i \frac{\left(R_{3} + \left[R_{4} \mid \mid R_{5}\right]\right)}{\left(R_{3} + \left[R_{4} \mid \mid R_{5}\right]\right) + \left(R_{6} + R_{7} + R_{8}\right)}\right]}_{i_{7}}^{R_{7}}.$$

(15)

Note especially that the ground connected to the upper end of the current source has no effect. The reasoning is as follows. To find  $e_0$ , we must find the current through  $R_7$ . When the current through  $R_7$  is known, the voltage across  $R_7$  is  $i_7R_7$ . Note that the current entering node A is i. If this is not obvious, note that the total current i must flow through  $R_9$ , but if it does, it must enter at node A because that is its only possible path. Knowing the current entering node A permits us to write the current divider equation to find  $i_7$ . The  $i_7R_7$  product yields  $e_0$ . Resistors  $R_1$ ,  $R_2$ ,  $R_9$ , and  $R_{10}$  do not enter into the equation because they have no effect on the current divider of interest.

Quite frequently, multiple current dividers occur in a single circuit. Example 6 demonstrates how to handle a multiple current divider.

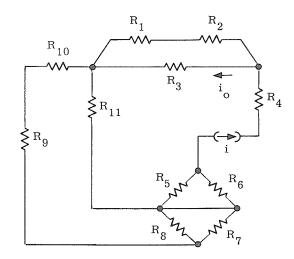

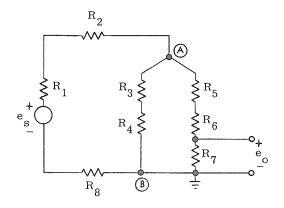

## Example 6

$\underline{\underline{\text{Problem--Determine e}}_{\text{O}} \text{ as a function of i and the resistors using current divider equations.}$  Write the answer in a single step.

#### Solution --

$$e_{o} = \underbrace{i}_{12} \left[ \frac{R_{12} + [R_{11} + \{(R_{3} + [R_{4}||R_{5}]) | (R_{6} + R_{7} + R_{8})\})]}_{i_{A}} \left[ \frac{(R_{3} + [R_{4}||R_{5}])}{(R_{3} + [R_{4}||R_{5}]) + (R_{6} + R_{7} + R_{8})} \right]}_{i_{7}} \right] R_{7}$$

(16)

To find  $i_7$ , the portion of i which flows through  $R_7$ , we must write two current divider fractions. Parentheses, braces, and brackets are used liberally in order to clarify the equations.

## Example 7

$\underline{\text{Problem--Determine e}}_{\text{O}} \text{ as a function of e}_{\text{S}} \text{ and the resistors using voltage divider equations.}$  Write the solution in a single step.

Solution--

$$e_{o} = e_{s} \left[ \frac{\left( \left[ R_{3} + R_{4} \right] \parallel \left[ R_{5} + R_{6} + R_{7} \right] \right)}{\left[ R_{1} + R_{2} + \left( \left[ R_{3} + R_{4} \right] \parallel \left[ R_{5} + R_{6} + R_{7} \right] \right) + R_{8}} \right] \left[ \frac{R_{7}}{R_{5} + R_{6} + R_{7}} \right]$$

$$V_{AB}$$

(17)

First, the fraction of  $e_s$  appearing between nodes (A) and (B) is found; then the portion of this voltage  $(V_{AB})$  appearing across  $R_7$  is determined. This amounts to writing a double voltage divider equation.

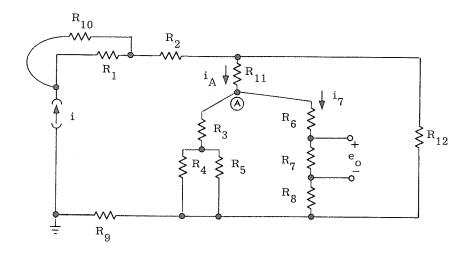

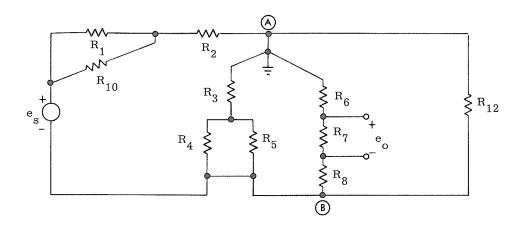

## Example 8

$\underline{\underline{Problem}}$ -Determine  $e_o$  as a function of  $e_s$  and the resistors using voltage divider equations. Write the solution in a single step.

Solution--

$$e_{o} = e_{s} \left[ \frac{\left[ \left( R_{12} \right) | \left( R_{3} + \left\{ R_{4} | R_{5} \right\} \right) | \left( R_{6} + R_{7} + R_{8} \right) \right]}{\left[ \left( R_{12} \right) | \left( R_{3} + \left\{ R_{4} | R_{5} \right\} \right) | \left( R_{6} + R_{7} + R_{8} \right) \right] + R_{2} + \left( R_{1} | R_{10} \right)}{\left[ R_{6} + R_{7} + R_{8} \right]} \right] \left[ \frac{R_{7}}{R_{6} + R_{7} + R_{8}} \right]$$

$$V_{AB}$$

(18)

## Superposition Theorem

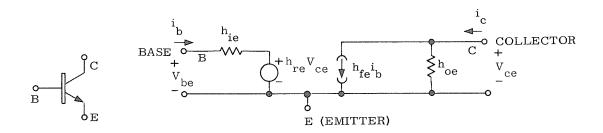

DPI analysis frequently requires application of the superposition theorem. This states that the voltage across, or the current through, any element can be computed in the following way: Replace all the <u>independent</u> generators except one by their internal impedances and compute the voltage across (or the current through) the element in question. Repeat this procedure for each independent generator in turn. Then, find the algebraic sum of all the calculated voltages across (or the currents through) the element in question; this will be the actual voltage across (or the current through) the element. Note especially that the generators that are replaced by their internal impedances are <u>independent</u> generators. An independent generator is one whose output is independent of any voltage or current in the circuit connected to the generator. When electronic circuits containing linear models of the active devices, e.g., bipolar transistors, FET's, etc., are analyzed, it is common practice to redraw the circuits, replacing the active devices with their associated linear equivalent circuits. Consider the common emitter hybrid equivalent circuit of an NPN transistor (Figure 5).

Figure 5. Hybrid Model of NPN Transistor Connected in Common-Emitter Configuration

This model contains a current-controlled current source and a voltage-controlled voltage source. The current source  $h_{fe}i_{b}$  is controlled by the  $i_{b}$  current, and the voltage source  $h_{re}V_{ce}$  is controlled by the  $V_{ce}$  voltage. Both of these sources are referred to as <u>dependent</u> generators because their outputs are dependent functions of a voltage or current which exists elsewhere in the circuit. If the superposition theorem is applied to such a circuit, these dependent generators are not replaced by their internal impedances but are retained throughout the analysis.

Only series parallel type networks will be investigated in the examples given in this section. Other types of networks which are not easily classified will be discussed in a later section.

Example 9 demonstrates the advantages of using the superposition theorem as opposed to loop or node analysis.

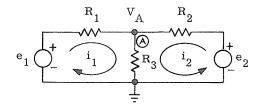

#### Example 9

<u>Problem</u> -- Determine  $V_A$  by using loop and node analysis and then by application of the superposition theorem; prove that the answers are the same by letting  $R_1$  =  $R_2$  =  $R_3$  = 1 $\Omega$ , and  $e_1$  =  $e_2$  = 1 V.

$\underline{\text{Loop Analysis--}} \text{Assume loop currents i}_1 \text{ and i}_2 \text{ flow as indicated.} \quad \text{Using Kirchhoff's voltage law (KVL), we sum the voltages around each loop.}$

$$i_1(R_1 + R_3) + i_2R_3 = e_1$$

(19)

$$i_1(R_3) + i_2(R_2 + R_3) = e_2$$

(20)

Equations (19) and (20) can be solved simultaneously for  $i_1$  and  $i_2$ ; then  $V_{\rm A}$  is found to be

$$V_A = (i_1 + i_2) R_3$$

Node Analysis -- Using Kirchhoff's current law (KCL) to sum the currents entering node (A), we have

$$\frac{e_1 - V_A}{R_1} + \frac{e_2 - V_A}{R_2} = \frac{V_A}{R_3}$$

$$\frac{e_1}{R_1} + \frac{e_2}{R_2} = V_A \left( \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3} \right)$$

$$V_{A} = \begin{pmatrix} \frac{e_{1}}{R_{1}} + \frac{e_{2}}{R_{2}} \\ \frac{1}{R_{1}} + \frac{1}{R_{2}} + \frac{1}{R_{3}} \end{pmatrix}$$

Superposition--Using superposition, we can write the answer in a single step by inspection.

$$V_{A} = e_{1} \underbrace{\begin{pmatrix} \begin{bmatrix} R_{3} & R_{2} \end{bmatrix} \\ R_{3} & R_{2} \end{bmatrix} + e_{2} \underbrace{\begin{pmatrix} \begin{bmatrix} R_{1} & R_{3} \end{bmatrix} \\ R_{1} & R_{3} \end{bmatrix} + R_{2} \end{pmatrix}}_{This part found by setting e_{2} to zero and using the voltage divider equation.}$$

$$(21)$$

Substituting the given values for resistance and voltage into the equations will prove the answers are the same, i.e.,  $V_A$  = 2/3  $V_\bullet$

The next example demonstrates the application of the superposition theorem to a circuit containing mixed sources.

#### Example 10

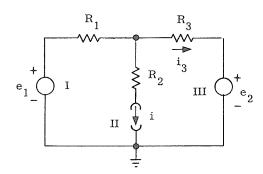

Problem -- Determine current i3 by application of the superposition theorem.

Solution—This circuit contains three independent generators; therefore, the contribution made to  $i_3$  by each generator can be found and the sum of these individual currents will yield the resultant current  $i_3$ .

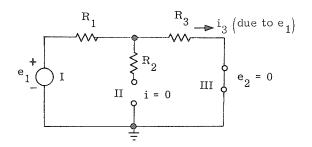

Step 1 -- Replace independent generators II and III by their internal impedances and determine the portion and direction of i<sub>3</sub> due to e<sub>1</sub> acting alone.

$$i_3 \left( \text{due to e}_1 \right) = \left( \frac{e_1}{R_1 + R_3} \right) \tag{22}$$

Note especially that an ideal independent current source is replaced by an infinite impedance (open circuit) and an ideal independent voltage source is replaced by zero impedance (short circuit).

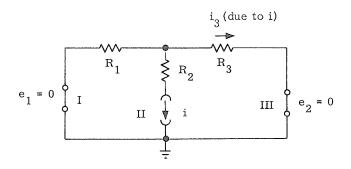

Step 2--Replace independent generators I and III by their internal impedances and determine the portion and direction of  $i_3$  due to i acting alone.

$$i_3$$

(due to i) =  $-i\left(\frac{R_1}{R_1 + R_3}\right)$  (current divider form) (23)

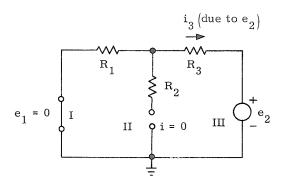

Step 3--Replace independent generators I and II by their internal impedances and determine the portion and direction of  $i_3$  due to  $e_2$  acting alone.

$$i_3 \text{ (due to } e_2) = -\left(\frac{e_2}{R_1 + R_3}\right)$$

(24)

Step 4-- The value of  $i_3$  is given by the algebraic sum of Equations (22), (23), and (24).

$$i_3 = \left(\frac{e_1}{R_1 + R_3}\right) - i\left(\frac{R_1}{R_1 + R_3}\right) - \left(\frac{e_2}{R_1 + R_3}\right)$$

(25)

Example 11 demonstrates how a dependent source can be handled by the superposition theorem.

## Example 11

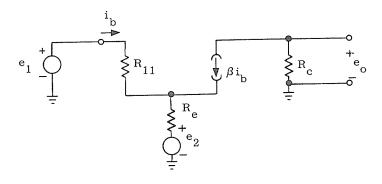

$\underline{\text{Problem}}\text{--Determine e}_{\text{O}} \text{ as a function of the independent sources e}_{1} \text{ and e}_{2}.$

## Solution--

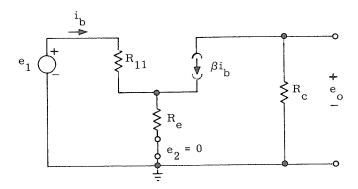

$\frac{\text{Step 1}}{\text{--Replace independent generator e}_2} \text{ by its internal impedance and determine}$  the portion of  $e_0$  due to source  $e_1$  acting alone.

First, we know  $e_0 = -\beta i_b R_c$  because all of the current from the dependent  $\beta i_b$  current generator flows through resistor  $R_c$ .

Writing the voltage drops around the R $_{11}$ , R $_{\rm e}$ , e $_{2}$ , e $_{1}$  loop and solving for i $_{\rm b}$ , we have

$$i_b (due to e_1) = \left(\frac{e_1}{R_{11} + (1 + \beta) R_e}\right)$$

.

So

$$e_{o} (due to e_{1}) = -\left(\frac{e_{1}}{R_{11} + (1+\beta)R_{e}}\right) \beta R_{c}$$

(26)

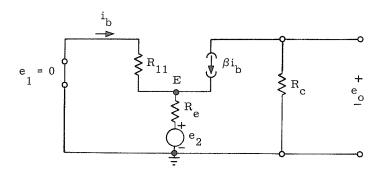

$\frac{\text{Step 2}-\text{Replace independent generator e}_1}{\text{tion of e}_0}$  due to e<sub>2</sub> acting alone.

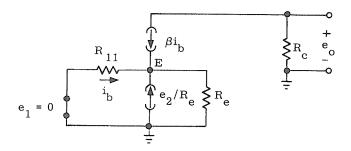

This circuit is best handled by replacing the R $_{\rm e}$ , e $_{\rm 2}$  combination by its Norton equivalent circuit, \* redrawing the circuit, and solving for i $_{\rm h}$ .

Applying the current divider equation at node E , we have

$$i_b = -\left[\beta i_b + \frac{e_2}{R_e}\right] \left(\frac{R_e}{R_e + R_{11}}\right)$$

Solving for i<sub>b</sub>,

$$i_b \left( \text{due to } e_2 \right) = - \left( \frac{e_2}{R_{11} + R_e (1 + \beta)} \right)$$

Now that the value of  $i_{\rm b}$  due to  ${\rm e}_2$  is known, we can substitute it into the expression for  ${\rm e}_{_{\rm O}}.$

<sup>\*</sup> Refer to Appendix A for a review of Norton's theorem.

$$e_{o} \text{ (due to } e_{2}) = -\beta i_{b} \text{ (due to } e_{2}) R_{c}$$

$$= \left[ \frac{e_{2}}{R_{11} + R_{e}(1+\beta)} \right] \beta R_{c}$$

(27)

$\underline{\text{Step 3}}\text{--The value of e}_{\text{O}}$  is given by the algebraic sum of Equations (26) and (27).

$$e_{o} = -\left(\frac{e_{1}}{R_{11} + (1+\beta)R_{e}}\right)\beta R_{c} + \left(\frac{e_{2}}{R_{11} + (1+\beta)R_{e}}\right)\beta R_{c}$$

(28)

The point to be emphasized in the solution of this circuit by application of the superposition theorem is that the dependent generator is <u>never</u> modified. Only the independent generators are replaced by their internal impedances.

Generally, the intermediate steps shown in Examples 9, 10, and 11 are omitted and the solutions are written in a single step.

#### Example 12

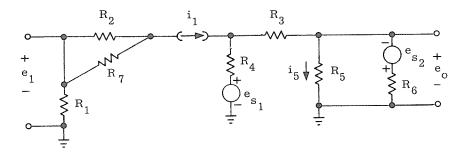

$\underline{\text{Problem}}\text{--Using the superposition theorem, derive expressions for } i_5$  and  $\mathbf{e}_1$  in a single step.

Solution--

$$e_{1} = -i_{1}R_{1}$$

$$e_{2} = \frac{R_{5} R_{6}}{R_{4} + R_{3} + (R_{5} R_{6})} \left(\frac{R_{6}}{R_{6} + R_{5}}\right) + e_{2} \left(\frac{R_{5} R_{6}}{R_{5} R_{6} + R_{3} + R_{4}}\right) \left(\frac{1}{R_{5}}\right)$$

$$e_{1} = -i_{1}R_{1}$$

$$e_{2} = -i_{1}R_{1}$$

$$e_{3} = -i_{1}R_{1}$$

$$e_{4} = -i_{1}R_{1}$$

$$e_{5} = -i_{1}R_{1}$$

$$e_{6} = -i_{1}R_{1}$$

$$e_{7} = -i_{1}R_{1}$$

$$e_{7} = -i_{1}R_{1}$$

$$e_{7} = -i_{1}R_{1}$$

$$e_{8} = -i_{1}R_{1}$$

$$e_{8} = -i_{1}R_{1}$$

$$e_{8} = -i_{1}R_{1}$$

$$e$$

## Driving-Point-Impedance (DPI) Equations

If the driving-point-impedance at each terminal of a bipolar transistor, FET, or vacuum tube (triode or pentode) operating in its linear region is known, the application of the aforementioned techniques will yield solutions to many electronic circuits in a single step. The analysis can be extended to the entire range of operation by utilizing break-point techniques. The expressions for the DPI seen at each terminal of a bipolar transistor, J-FET and (triode or pentode) vacuum tube will now be derived. For the sake of brevity, little will be said about the circuit models except that the implied assumptions made in using these models have proved to be sufficiently accurate for most engineering calculations where internal device capacitances can be ignored. 2

#### Bipolar Transistor DPI Equations

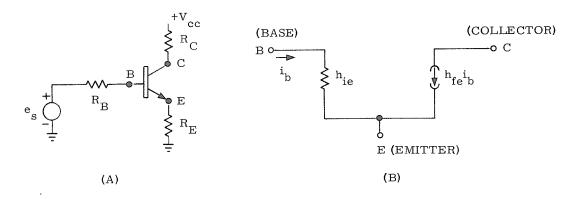

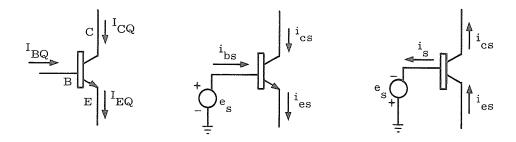

The circuit shown in Figure 6 (A), along with the simplified hybrid model of the transistor in the common-emitter configuration (Figure 6B)<sup>2</sup>, will be used to derive expressions for the DPI seen looking into each terminal of the bipolar transistor.

Figure 6. Circuit for Determination of Bipolar Transistor DPI Equations

If the simplified hybrid model of the transistor shown in Figure 6 (B) is compared with the complete hybrid model of Figure 5, it can be seen that the  $h_{oe}$  and  $h_{re}$  parameters have been omitted. In practice these parameters are usually not specified on data sheets. Their inclusion in the hybrid model unduly complicates the circuit analysis and provides no benefits to speak of.  $h_{ie}$  is defined as the dynamic base-to-emitter resistance, and  $h_{fe}$  is defined as the dynamic small signal forward current gain.  $h_{fe}$  is usually referred to as the beta  $(\beta)$  of the transistor. All of the small signal parameters are defined at the quiescent operating point chosen for the device.

$$h_{ie} = \frac{\partial v_{be}}{\partial i_{b}} \begin{vmatrix} Base-to-emitter impedance at quiescent operating point (ohms) \\ v_{ce} = Constant \end{vmatrix} v_{ce} = \frac{\partial v_{be}}{\partial i_{b}} \begin{vmatrix} Base-to-emitter impedance at quiescent operating point (dimensionless) \\ v_{ce} = Constant \end{vmatrix} v_{ce}$$

$h_{ie}$  and  $\beta$  are the only two parameters that will be used in the analysis of transistor circuits using the DPI technique, as opposed to the more conventional approach of using common-emitter, common-collector, and common-base hybrid parameters. Although  $h_{ie}$  can be measured on a curve tracer, a useful formula for determining  $h_{ie}$  at room temperature is given by Equation (31).

$$h_{ie} \approx \frac{26 \times 10^{-3} (1 + \beta)}{I_{EQ}}$$

(31)

where  $\boldsymbol{I}_{\mathrm{EO}}$  is the quiescent emitter current expressed in amperes.

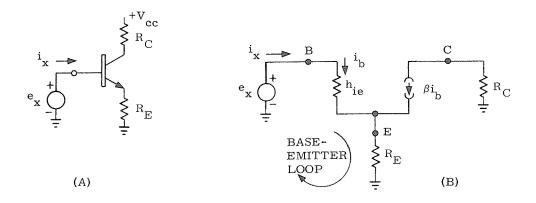

First, the DPI seen looking into the base terminal of the transistor will be found. The DPI seen by the  $e_s$  signal source (Figure 6A) is  $R_B$  in series with the base DPI of transistor  $Q_1$ . Recognizing this fact permits us to move over to the base and drive it with an external generator, and then find the base DPI by solving for the current flowing from the external generator. This scheme is shown in the circuit of Figure 7 where base DPI =  $\frac{e_x}{i_y}$ .

Figure 7. Base DPI of Bipolar Transistor

Using Kirchhoff's voltage law (KVL) around the base-emitter loop (Figure 7B), we have

$$i_b h_{ie} + i_b R_E + \beta i_b R_E - e_x = 0.$$

(32)

Observing  $i_b = i_x$  and solving for base DPI =  $\frac{e_x}{i_x}$  produces

$$\begin{vmatrix} \frac{e}{x} \\ \frac{i}{x} \end{vmatrix} = \text{base DPI} = h_{ie} + (1+\beta)R_{E}$$

(33)

Equation (33) can be interpreted as meaning that any impedance ( $R_E$ ) in the emitter lead of a bipolar transistor, when measured at the base terminal, will be increased by the factor (1 +  $\beta$ ).

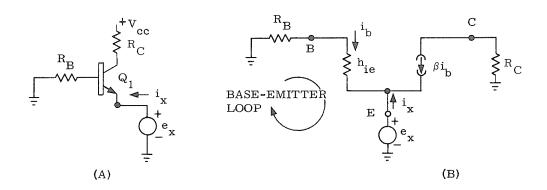

The DPI seen looking into the emitter terminal of the bipolar transistor can be determined by driving the emitter with an external voltage source and solving for the generator current. The circuit is shown in Figure 8.

Figure 8. Emitter DPI of Bipolar Transistor

Using Kirchhoff's current law (KCL) at the emitter node and writing the KVL equation around the base-emitter loop will yield emitter DPI =  $\frac{e_X}{i_y}$ .

$$i_{x} + i_{b} + \beta i_{b} = 0.$$

$$i_{x} = -i_{b}(1 + \beta)$$

(34)

and

$$(h_{ie} + R_B)i_b + e_x = 0$$

$$i_b = -\frac{e_x}{h_{ie} + R_B}$$

(35)

So

$$\frac{e_{x}}{i_{x}} = \text{emitter DPI} = \frac{h_{ie} + R_{B}}{(1+\beta)}$$

(36)

Equation (36) indicates that <u>any impedance</u> ( $R_B$ ) connected to the base, as seen at the emitter, is diminished by the (1+ $\beta$ ) factor.

The same procedure can be used to determine the collector DPI. From the simplified hybrid circuit model of the transistor (Figure 6B), it should be evident that the collector DPI is infinite since an external voltage source connected to the collector cannot excite a base current; therefore, the output from the  $\beta i_b$  generator will be zero.

Equations (33), (36), and (37) are fundamental to DPI analysis of bipolar transistor circuits. Summarizing, we have

Base DPI =

$$h_{ie} + (1+\beta)R_{E}$$

(33)

Emitter DPI =  $\frac{h_{ie} + R_{B}}{(1+\beta)}$  (36)

Collector DPI =  $\infty$  (37)

The key to effectively applying these equations is to remember that the impedances  $R_B$  and  $R_E$  are the impedances seen by the base and emitter of the bipolar transistor respectively.  $R_B$  and  $R_E$  quite frequently are combinations of other circuit elements including transistors, FET's, etc. In addition to the DPI Equations, the basic relations between the base, emitter and collector currents of a bipolar transistor are indispensible to the analysis. These important relations are given below.

$$i_{c} = \beta i_{b}$$

$$i_{e} = (1+\beta)i_{b}$$

$$i_{c} = \left(\frac{\beta}{1+\beta}\right)i_{e}$$

(38)

Before DPI analysis is applied to an actual circuit, the DPI equation for a triode or pentode vacuum tube and J-FET will be derived. Note that these techniques are also applicable to the derivation of the DPI equations of other active devices.

## Triode/Pentode Vacuum Tube DPI Equations

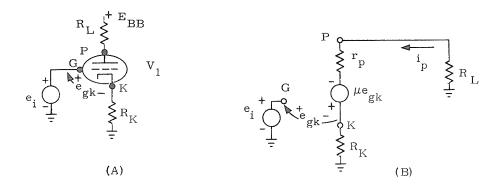

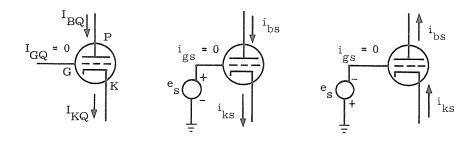

Figure 9 illustrates the circuit to be used for the determination of the vacuum tube DPI equations.

Figure 9. Circuit for the Determination of Vacuum Tube DPI Equations

$r_p$  is the dynamic plate resistance and  $\mu$  is the forward voltage amplification factor. Both of these parameters are defined at the quiescent operating point chosen for the tube.

$$r_{p} = \frac{\partial v_{pk}}{\partial i_{p}} \quad | \quad \text{(ohms)}$$

$$v_{gk} = \text{Constant}$$

$$\mu = \frac{-\partial v_{pk}}{\partial v_{gk}} \quad | \quad \text{(dimensionless)}$$

$$i_{p} = \text{Constant}$$

Inspection of the equivalent circuit of Figure 9(B) shows that the grid DPI is infinite (no grid current flows).

Before the other equations are derived, an expression for the signal plate current will be found. This equation will be used frequently in the application of DPI analysis. Writing the KVL equation around the plate-cathode circuit (Figure 9B), we have

$$i_p r_p + i_p R_L + i_p R_K - \mu e_{gk} = 0$$

(42)

but

$$e_{gk} = e_i - i_p R_K . (43)$$

Substituting Equation (43) into (42) gives

$$i_p r_p + i_p R_L + i_p R_K - \mu e_i + \mu i_p R_K = 0$$

$$i_{p} = \left(\frac{\mu e_{i}}{R_{L} + r_{p} + (1+\mu)R_{K}}\right)$$

(44)

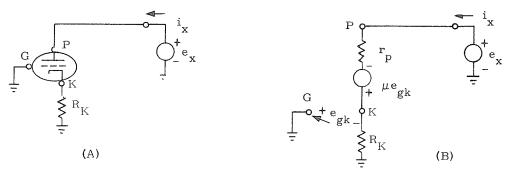

To determine the plate DPI, we apply an external voltage source to the plate and find the current flow from this source as shown in Figure 10.

Figure 10. Determination of Plate DPI

Writing the KVL equation around the plate-cathode circuit, we have

$$i_{x}r_{p} - \mu e_{gk} + i_{x}R_{K} - e_{x} = 0$$

(45)

But

$$e_{gk} = -i_{x}^{R}K (46)$$

Substituting Equation (46) into (45) and solving for plate DPI =  $\frac{e}{x}$ , we have

$$i_{x}r_{p} - \mu(-i_{x}R_{K}) + i_{x}R_{K} = e_{x}$$

$$\frac{e_{x}}{i_{x}} = \text{plate DPI} = r_{p} + (1+\mu)R_{K}$$

(47)

Equation (47) indicates that <u>any impedance</u>  $(R_{K})$  connected to the cathode, as seen at the plate, is increased by the  $(1+\mu)$  factor.

The cathode DPI is found in a similar manner using the circuit of Figure 11.

Figure 11. Determination of Cathode DPI

Writing the KVL equation around the plate-cathode circuit, we have

$$\mu e_{gk} + i_x r_p + i_x R_L - e_x = 0$$

(48)

But

$$e_{gk} = -e_{x} (49)$$

Substituting Equation (49) into (48) and solving for the cathode DPI =  $\frac{e_x}{i_x}$ , we have

$$-\mu e_{x} + i_{x} (r_{p} + R_{L}) - e_{x} = 0$$

$$\frac{e_{x}}{i_{x}} = \text{cathode DPI} = \left(\frac{r_{p} + R_{L}}{1 + \mu}\right)$$

(50)

Equation (50) indicates that <u>any impedance</u> ( $R_L$ ) connected to the plate, as seen at the cathode, is diminished by the (1+ $\mu$ ) factor.

In summary, we have

$$i_{p} = \left(\frac{\mu e_{i}}{R_{L} + r_{p} + (1+\mu)R_{K}}\right)$$

(44)

$$Grid DPI = \infty$$

(41)

$$Plate DPI = (r_{p} + [1+\mu]R_{K})$$

(47)

$$Cathode DPI = \left(\frac{r_{p} + R_{L}}{1+\mu}\right)$$

(50)

Here, as in the case of the bipolar transistors, the important point to remember is that the  $R_{L}^{}$  and  $R_{K}^{}$  impedances can be other circuits containing active devices, i.e., transistors, vacuum tubes, etc.

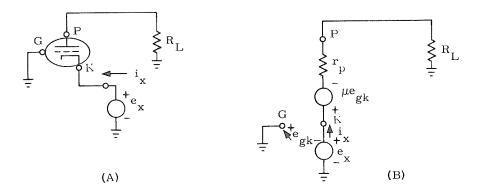

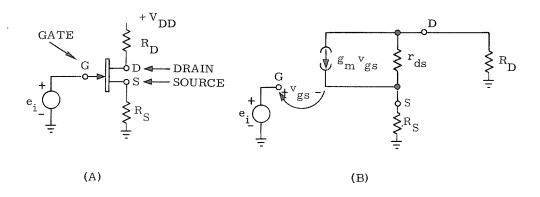

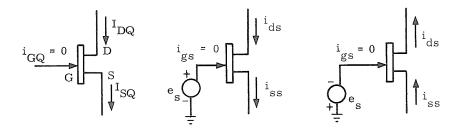

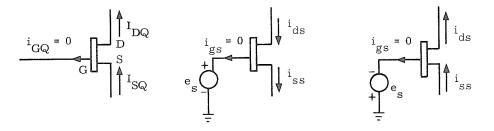

#### J-FET DPI Equations

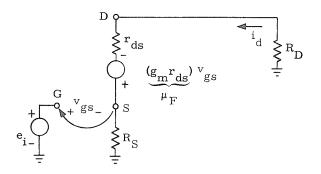

The circuit shown in Figure 12 will be used to derive the DPI equations for a J-FET (junction field-effect transistor). The operating region is defined such that no gate current flows.

Figure 12. Circuit for Determination of J-FET DPI Equations

The FET equivalent circuit of Figure 12(B) can be made to assume the same form as the triode vacuum tube equivalent circuit of Figure 9(B) by the application of Thevenin's Theorem as shown in Figure 13.

$<sup>^</sup>st$ Refer to Appendix A for a review of Thevenin's Theorem.

Figure 13. Thevenin Equivalent of FET Equivalent Circuit

Now if we define a voltage amplification factor  $\mu$  for the FET such that

$$\mu_{F} = g_{m} r_{ds} \tag{51}$$

then the DPI equations for the FET take on exactly the same form as the triode vacuum tube equations and the same remarks apply. The FET DPI equations follow:

$$i_{d} = \left(\frac{\mu_{F}e_{i}}{R_{D} + r_{ds} + (1 + \mu_{F})R_{S}}\right)$$

(52)

$$Gate DPI = \infty$$

$$Source DPI = \frac{r_{ds} + R_{D}}{(1 + \mu_{F})}$$

(54)

Gate DPI =

$$\infty$$

(53)

Source DPI =

$$\frac{r_{ds} + R_{D}}{(1 + \mu_{F})}$$

(54)

Drain DPI =

$$r_{ds} + (1+\mu_{\overline{F}}) R_{S}$$

(55)

$r_{\rm ds}$  is the dynamic drain-to-source resistance and corresponds to  $r_{\rm p}$  of the vacuum tube.  $\mu_{\rm F}$  is the voltage amplification factor, and  $\mathbf{g}_{\mathbf{m}}$  is the transconductance of the FET. These parameters are defined in the same manner as they are for the triode vacuum tube, i.e.,

$$\mu_{F} = \frac{-\partial v_{ds}}{\partial v_{gs}} \begin{vmatrix} (dimensionless) \\ i_{d} = Constant \end{cases}$$

(57)

These parameters are all defined at the quiescent operating point.

In most cases,  $r_{ds}$  can be assumed to be infinite. This greatly simplifies the DPI equations for the FET. The effect of letting  $r_{ds}$  go to infinity can be seen by substituting the expression for  $\mu_{F}$  (Equation 51) into Equations (52), (54), and (55) and taking the limit as  $r_{ds}$  goes to infinity.

$$\lim_{r_{ds} \to \infty} i_{ds} = \lim_{r_{ds} \to \infty} \left( \frac{g_{m} r_{ds} e_{i}}{R_{D}^{+} r_{ds}^{+} (1 + g_{m} r_{ds}^{-}) R_{S}} \right) = \left( \frac{e_{i}}{R_{D}^{+} r_{ds}^{-}} + \frac{e_{i}^{-}}{R_{D}^{-} r_{ds}^{-}} + \frac$$

A summary of the ideal FET equations follows:

$$i_{d} = \frac{e_{i}}{\frac{1}{g_{m}} + R_{S}}$$

$$Gate DPI = \infty$$

$$Source DPI = \frac{1}{g_{m}}$$

$$Drain DPI = \infty$$

$$(52-A)$$

$$IDEAL$$

FET DPI EQUATIONS

$$(53)$$

In the examples that follow, both sets of equations will be used but it should be emphasized that in most cases, the ideal FET equations are sufficient for most engineering calculations.

## Application of DP1 Analysis to Some Simple Transistor Circuits

#### Series Parallel Networks

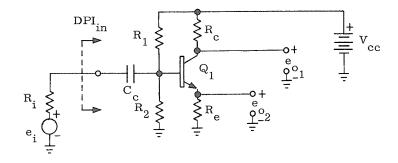

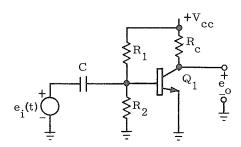

All of the basic tools needed to effectively apply DPI analysis to a wide variety of electronic circuits have been covered. A sampling of how DPI analysis can be utilized on a variety of circuits will now be presented. Feedback circuits will be covered later. The first circuit to be analyzed is shown in Figure 14.

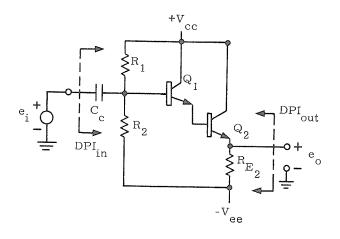

Figure 14. Single Stage Transistor Amplifier

Assume that the DPI looking in at the input and both output ports, and also the voltage gains, are required. The input DPI is the capacitive reactance of  $C_c$  in series with the parallel combination of  $R_1$ ,  $R_2$  and the base DPI of  $Q_1$ . The complete expression for the DPI seen by the signal source is given in Equation (59), which was written in a single step by inspection.

$$DPI_{in} = \left(\frac{1}{j\omega C_{c}}\right) + \left(R_{1} \| R_{2}\right) \| \underbrace{\left(h_{ie} + \left[1 + \beta\right] R_{e}\right)}_{Base DPI}$$

(59)

The DPI at the e terminal is  $R_c$  since the collector DPI =  $\infty$ .

$$DPI e_{O_1} = R_{C}$$

(60)

The DPI at the e terminal is  $R_{\rm e}$  in parallel with the emitter DPI.

DPI

$$e_{O_2} = (R_e) \parallel \left\{ \frac{h_{ie} + (R_1 \parallel R_2) \parallel (\frac{1}{j\omega C_c} + R_i)}{(1+\beta)} \right\}$$

Emitter DPI

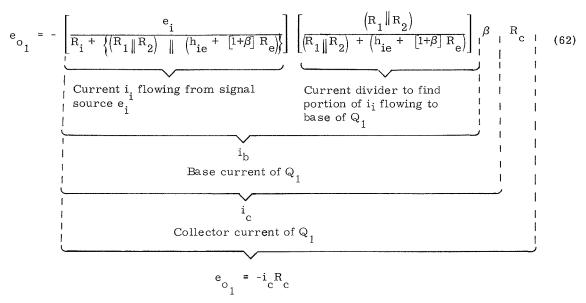

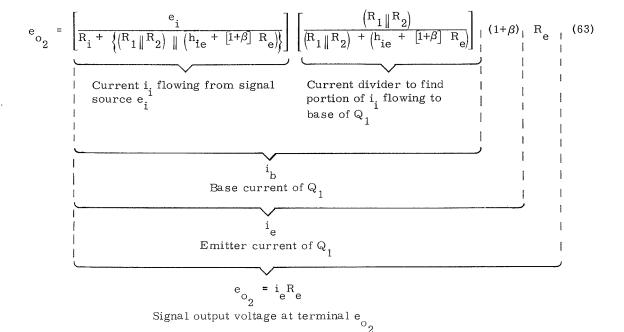

If only mid-band frequencies are considered, the capacitive reactance terms in Equations (59) and (61) can be dropped. The mid-band signal voltage gains  $\frac{e_0}{e_1}$  and  $\frac{e_0}{e_1}$  will be written by inspection.  $+V_{cc}$  is always assumed to be at signal ground.

Signal output voltage at terminal e

Equations (62) and (63) are derived as follows. The signal output voltage is determined by the current flowing through the load impedance ( $R_c$  or  $R_e$  for  $e_0$  or  $e_0$ ). Both the emitter and collector signal currents depend upon the signal base current, but the signal base current is determined by the total current flowing from the signal source  $e_i$ ; therefore, to find either the emitter or collector signal current, the first step is to find the total signal current  $i_i$  that flows from the  $e_i$  signal source. Once  $i_i$  is known, a current divider fraction can be written to determine what portion of  $i_i$  flows into the base of  $Q_1$ . With the base current known, the collector or emitter current can be found by multiplying by  $\beta$  or  $(1+\beta)$  respectively. The last step is, of course, to multiply by the respective load impedance,  $R_c$  or  $R_c$ . The correct phase must be determined by tracing the currents through the circuit, e.g., a current into the base of  $Q_1$  causes a current into the collector of  $Q_1$ , which causes  $e_0$  to decrease with respect to ground; thus, there is a  $180^\circ$  phase reversal as noted in Equation (62). It should be obvious at this point that it is far more tedious to explain DPI analysis than it is to apply it.

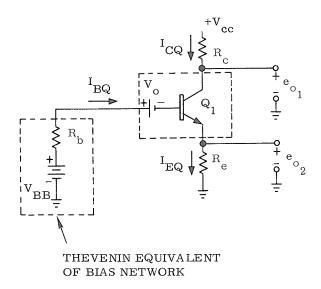

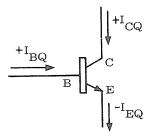

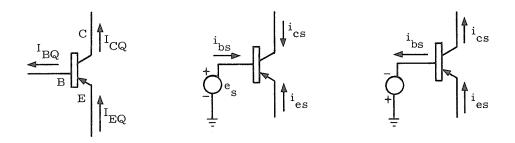

The dc quiescent conditions existing in the circuit of Figure 14 can also be determined with DPI analysis. The dc analysis of bipolar transistor circuits requires that the base-emitter dc offset voltage be taken into consideration. If silicon transistors are being used, the offset voltage is in the range of 0.6 to 0.7 volt. The dc circuit of the single stage amplifier (Figure 14) is shown in Figure 15 with the R<sub>1</sub>, R<sub>2</sub> bias network replaced by its Thevenin's equivalent circuit.

Figure 15. DC Circuit of Single-Stage Amplifier

Note that the dc offset voltage of the base-emitter junction is treated as if it were a battery connected in series with the base terminal.

To find the quiescent base current  $I_{\text{BQ}}$ , we write the KVL equation around the base-emitter loop using the fact that we know the base DPI of  $Q_1$ .

$$I_{BQ}\left(R_{b}\left[+\ h_{ie}+(1+\beta)R_{e}\right]\right)+V_{o}-V_{BB}=0$$

$$I_{BQ} = \left(\frac{V_{BB} - V_{o}}{R_{b} + h_{ie} + (1+\beta)R_{e}}\right)$$

(64)

Recalling that  $I_{CQ} = \beta I_{BQ}$  and  $I_{EQ} = (1+\beta)I_{BQ}$ , we have expressions for all of the quiescent currents; knowing these currents permits us to write the expressions for the quiescent output voltages as shown in Equations (65) and (66).

$$E_{o1Q} = V_{CC} - I_{CQ}R_{c}$$

(65)

$$E_{O2Q} = I_{EQ}^{R} e \tag{66}$$

At this point, a note about biasing the circuit of Figure 14 is in order. Good design practice demands that the values of  $E_{o1Q}$  and  $E_{o2Q}$  (quiescent values of output voltage) remain relatively constant for a wide range of  $\beta$ 's. In other words, the value of quiescent collector current should be as independent of  $\beta$  as is possible to permit changing the transistor without having to alter the circuit components. It seems to be common practice to use "rules of thumb" for biasing circuits. Unfortunately, it is also quite common to find designers applying these rules to circuits or under conditions where the original assumptions do not apply. Circuit equations are so simple to derive utilizing DPI analysis that it is easier to write and analyze the equations of interest than it is to remember "handy-dandy" formulas.

As an example, let us consider what conditions must be met in order to maintain a constant  $I_{CQ}$  in the circuit of Figure 15. By multiplying the expression for the quiescent base current (Equation 64) by  $\beta$ , we have an expression for  $I_{CQ}$ .

$$I_{CQ} = \beta I_{BQ} = \beta \left( \frac{V_{BB} - V_{o}}{R_{b} + h_{ie} + (1+\beta)R_{e}} \right)$$

$$(67)$$

Manipulating Equation (67) yields

$$I_{CQ} = \frac{\left(V_{BB} - V_{o}\right)}{\left[\frac{R_{b} + h_{ie}}{\beta}\right] + \left[\frac{(1+\beta)}{\beta} R_{e}\right]}$$

(68)

Now, we must examine Equation (68) in order to see how we can force it to be independent of  $\beta$ . Examining the denominator, we see that two terms are a function of  $\beta$ . It is usually a good approximation to assume that  $\frac{(1+\beta)}{\beta}\approx 1$  for high  $\beta$  transistors, i.e., if  $\beta$  = 40, then 41/40 = 1.025  $\approx$  1.0. If we make this assumption, the denominator term containing  $R_e$  is

relatively independent of  $\beta$ . It is also easy to see that if  $R_e$  is made much much greater than  $\frac{R_b + h_i}{\beta}$ , Equation (68) will be relatively independent of  $\beta$ . Furthermore, it is usually valid to assume that  $h_{ie}/\beta$  is small enough compared to  $R_b/\beta$  that the former can be left out of the expression. We then have  $R_e >> \frac{R_b}{\beta}$  or  $\beta R_e >> R_b$  for good stability of  $I_{CQ}$ .

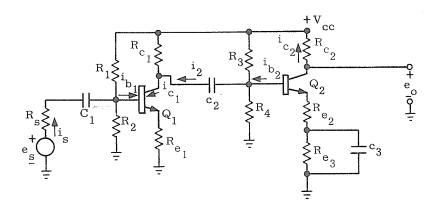

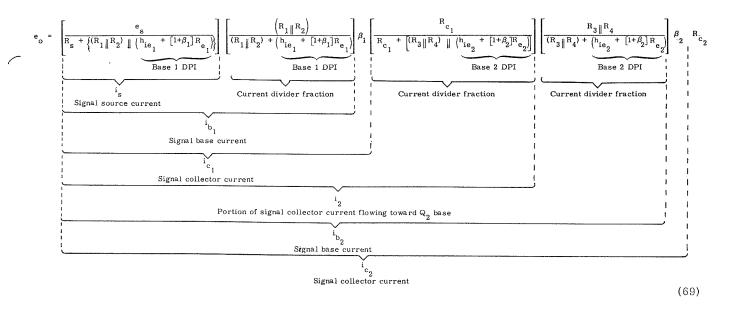

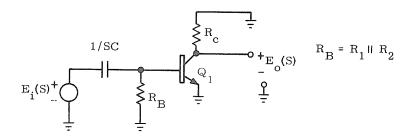

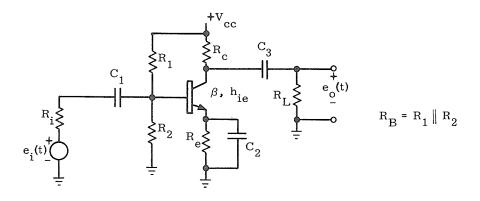

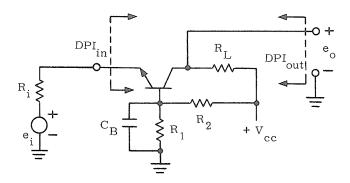

As a further example, consider the circuit shown in Figure 16 and determine the mid-band voltage gain by writing the solution in a single step. At mid-band frequencies the coupling and by-pass capacitors can be considered to be signal short circuits. The voltage gain expression is given in Equation (69).

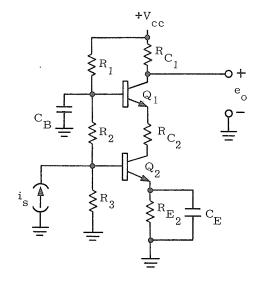

Figure 16. Two-Stage RC Coupled Amplifier

Equation (69) is developed as follows. The signal output voltage  $e_0$  is produced by  $i_{c_2}$  flowing through  $R_{c_2}$ , but  $i_{c_2}$  is determined by  $i_{b_2}$ . The signal base current  $i_{b_2}$  is a fraction of  $i_{c_1}$ ,

but  $i_{c_1}$  is determined by  $i_{b_1}$ , which, in turn, is a fraction of the signal source current  $i_s$ .  $i_s$  is, of course, determined by  $e_s$ , the signal source. When writing the expression for  $e_o$  as a function of  $e_s$ , the first step is to determine the signal source current  $i_s$ . With  $i_s$  known,  $i_{b_1}$  can be found by multiplying  $i_s$  by a current divider fraction to determine the portion of  $i_s$  which flows to the base of  $Q_1$ .  $i_{c_1}$  is  $\beta i_{b_1}$ , and  $i_2$  can be found by multiplying by another current divider fraction. An additional current divider fraction produces the  $i_{b_2}$  signal base current, and  $i_{c_2}$  is given by the  $\beta i_{b_2}$  product. Finally,  $e_o$  is found by multiplying by  $R_{c_2}$ .

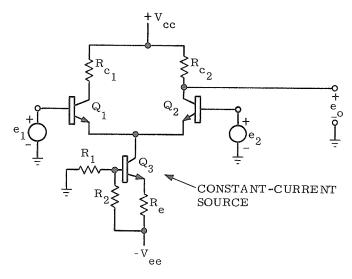

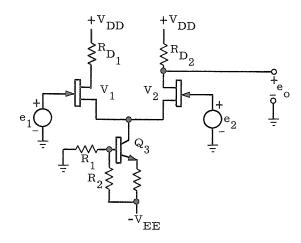

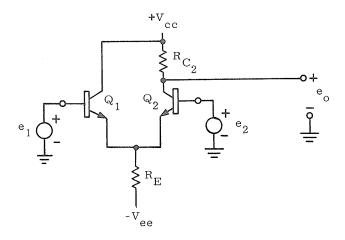

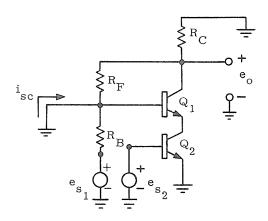

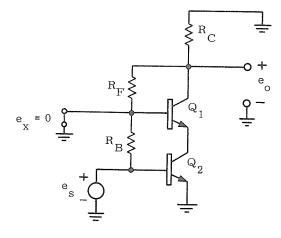

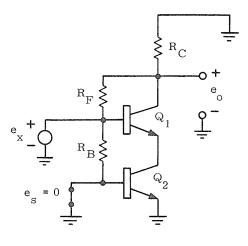

A basic building block of many integrated and discrete circuits is the emitter-coupled differential amplifier shown in Figure 17.

Figure 17. Basic Emitter-Coupled Differential Amplifier

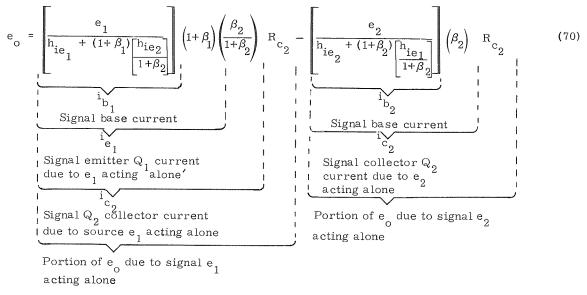

Using DPI analysis and the superposition theorem, the output voltage as a function of the two input voltages can be written by inspection. The result is shown in Equation (70).

To obtain Equation (70) we utilize the superposition theorem. We replace voltage signal source  $\mathbf{e}_2$  by its internal impedance (short circuit) and solve for the portion of  $\mathbf{e}_0$  which is caused by signal source  $\mathbf{e}_1$ ; then, voltage signal source  $\mathbf{e}_1$  is replaced by its internal impedance (short circuit), and the portion of  $\mathbf{e}_0$  which is caused by signal source  $\mathbf{e}_2$  is found. The sum of these two terms gives the output voltage  $\mathbf{e}_0$  as a function of the two input signals  $\mathbf{e}_1$  and  $\mathbf{e}_2$  and the circuit parameters. Setting  $\mathbf{e}_2 = 0$  we find the current flowing from the  $\mathbf{e}_1$  signal source which is the signal base current of  $\mathbf{Q}_1$ . The signal emitter current of  $\mathbf{Q}_1$  is found by multiplying  $\mathbf{i}_{\mathbf{b}_1}$  by  $(1+\beta_1)$ . All of the signal emitter current of  $\mathbf{Q}_1$  flows into the  $\mathbf{Q}_2$  emitter since the DPI of collector  $\mathbf{Q}_3$  is infinite. Collector  $\mathbf{Q}_2$  signal current is  $\left(\beta_2/(1+\beta_2)\right)$  times the  $\mathbf{Q}_2$  signal emitter current. Multiplying the whole expression by collector load  $\mathbf{R}_{\mathbf{C}_2}$  yields the portion of  $\mathbf{e}_0$  due to  $\mathbf{e}_1$ . Setting  $\mathbf{e}_1 = 0$  we find the current flowing from the  $\mathbf{e}_2$  signal source which is the signal base current of  $\mathbf{Q}_2$ . Multiplying the signal base current of  $\mathbf{Q}_2$  by  $\mathbf{g}_2$  produces the signal collector current of  $\mathbf{Q}_2$ , and multiplying by  $\mathbf{R}_{\mathbf{C}_2}$  produces the portion of  $\mathbf{e}_0$  due to  $\mathbf{e}_2$ . Checking current directions will show that  $\mathbf{e}_1$  is connected to the noninverting side of the amplifier while  $\mathbf{e}_2$  is connected to the inverting side.

The circuit of Figure 18 is an FET source-coupled differential amplifier using FET's in place of the transistors  $Q_1$  and  $Q_2$  of Figure 17. The voltage gain of this amplifier is given in Equation (71) without further explanation. The reasoning process is very similar to that used for deriving the gain of the circuit of Figure 17.

Figure 18. Basic Source-Coupled Differential Amplifier

$$e_{o} = \left\{ \frac{\frac{\mu_{F_{1}}^{e_{1}}}{\left( \left( \frac{1}{r_{ds_{1}} + R_{D_{1}} + (1 + \mu_{F_{1}})} \left( \frac{r_{ds_{2}} + R_{D_{2}}}{(1 + \mu_{F_{2}})} \right) \right)}{\left( \frac{r_{ds_{1}} + R_{D_{1}} + (1 + \mu_{F_{1}})}{(1 + \mu_{F_{1}})} \right) \left( \frac{r_{ds_{1}} + R_{D_{2}}}{(1 + \mu_{F_{2}})} \right) \right\}} R_{D_{2}}$$

$$(71)$$

If the ideal FET equations are applied to the solution of this circuit, the expression for e o is given in Equation (71-A). It can be seen that utilization of the ideal FET DPI equations greatly simplifies the form of the resulting circuit solutions.

$$e_{o} = \left\{ \frac{e_{1}}{\frac{1}{g_{m1}} + \frac{1}{g_{m2}}} \right\} R_{D_{2}} - \left\{ \frac{e_{2}}{\frac{1}{g_{m2}} + \frac{1}{g_{m1}}} \right\} R_{D_{2}}$$

(71-A)

$$= (e_1 - e_2) \left\{ \frac{R_{D_2}}{\frac{1}{g_{m1}} + \frac{1}{g_{m2}}} \right\}$$

(71-B)

The form of Equation (71-B) clearly demonstrates why this amplifier is called a difference amplifier.

#### Nonseries Parallel Networks

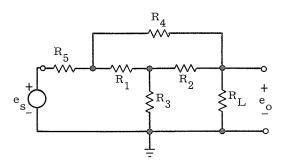

Thus far, only simple series parallel type networks have been used as examples. Quite frequently, networks are encountered which can not be so easily classified. Consider the circuit shown in Figure 19 and observe that neither the voltage divider nor the current divider equation will permit the answer to be written directly by inspection. Of course, conventional node or loop analysis techniques will yield the desired answer, but our object is to avoid this approach because the form of the resultant equations is not as clear and easily interpreted as are voltage or current divider equations.  $\Delta$  - Y transformations will also be avoided because they are not readily performed in a single step, and rarely are they remembered. The object here will be to familiarize the reader with a technique which can be applied to the solution of circuits containing feedback.

Figure 19. Simple Nonseries Parallel Circuit

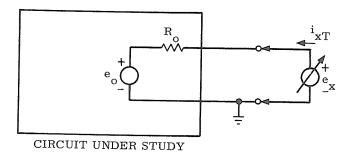

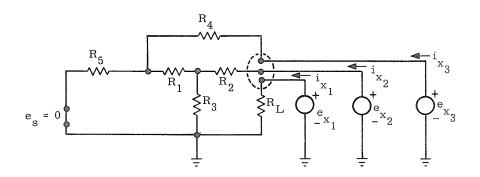

The circuit of Figure 20 is the same as the one shown in Figure 19 except for the addition of the e\_voltage generator to the e\_terminal.

Figure 20. Simple Nonseries Parallel Circuit

An expression for  $e_0$  can be easily found by using superposition. Solve for the current  $i_{xT}$  by using the superposition theorem;  $i_{xT}$  will be composed of two parts:

$$i_{xT} = (e_s, e_x = 0) + i_x (e_s = 0, e_x)$$

(72)

The first part of  $i_{xT}$  is due to  $e_x$  when  $e_x$  = 0, and the second part is due to  $e_x$  when  $e_x$  = 0.

Several things should be noted about Equation (72). When  $e_{_{\rm S}}$  = 0,  $i_{_{\rm X}}$  due to  $e_{_{\rm X}}$  has the form

$$i_x(e_x) = \frac{e_x}{(factor)}$$

.

Dimensional analysis will reveal that the (factor) must be an impedance, and, in fact, the (factor) turns out to be the output driving-point-impedance seen looking into the output terminals. When  $e_x = 0$ ,  $i_x$  due to  $e_s$  is the output short circuit current. Equation (72) can now be rewritten as

$$i_{xT} = i_{osc} + \frac{e_x}{R_o}$$

(73)

where  $i_{OSC}$  is the output short circuit current, and  $R_O$  is the output driving-point-impedance. Because  $e_X$  is a ficticious external generator, it can be adjusted to assume any convenient value. If  $e_X$  is adjusted so that it assumes the value of  $e_O$ , this forces the current flowing from the  $e_X$  generator to be zero. If this is not obvious, consider the circuit of Figure 21.

Figure 21.

As soon as the e generator is adjusted so that e = e o,  $i_{xT}$  will be forced to zero and removing e will have no effect. Applying the superposition theorem to the circuit of Figure 21 and solving for  $i_{xT}$ , we have

$$i_{xT} = \frac{e_x}{R_o} - \frac{e_o}{R_o}$$

(74)

Setting  $e_x = e_0$  forces  $i_{xT} = 0$ .

Assume now that we have set  $e_x = e_0$  such that  $i_{xT} = 0$ . This forces Equation (73) to become

$$0 = i_{osc} + \frac{e_{o}}{DPI_{out}}$$

(75)

Now Equation (75) can be solved for  $e_0$ ,

$$e_{o} = -i_{osc} DPI_{out}$$

(76)

where the R<sub>o</sub> term has been replaced by the more descriptive DPI<sub>out</sub> term. The method used to derive Equation (76) should be thoroughly understood because it is the basis for handling feedback circuits using DPI analysis. This method will now be used to solve the circuit of Figure 20, which is repeated in Figure 22. The answer will be developed in steps to demonstrate the technique.

Figure 22. Simple Nonseries Parallel Circuit

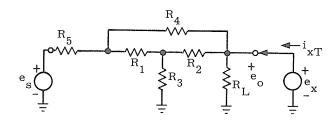

$i_{xT} = i_{osc} + \frac{e_x}{DPI_o}$  by the superposition theorem. Solving for  $i_{osc}$  shown in Figure 23, we have Equation (77).

Figure 23. Solving for Current i osc

$$i_{osc} = \left\{ \frac{e_{s}}{R_{5} + \left[R_{4} \right] \left\{R_{1} + \left(R_{2} \right] R_{3}\right\}} \right\} \left\{ -\left( \frac{R_{1} + \left[R_{2} \right] R_{3}}{\left[R_{1} + \left[R_{2} \right] R_{3}\right] + R_{4}} - \left( \frac{R_{4}}{R_{4} + \left(R_{1} + \left[R_{2} \right] R_{3}\right)} \right) \left( \frac{R_{3}}{R_{2} + R_{3}} \right) \right\} \right\}$$

$$Total current i_{s} from e_{s}$$

$$Portion of i_{s} flowing through R_{4} and contributing to i_{osc}.$$

$$Portion of i_{s} flowing through R_{2}$$

and contributing to i\_osc.

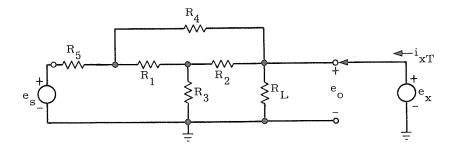

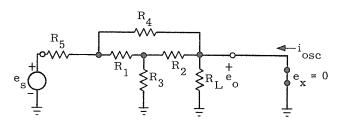

Now we solve for the other part of  $i_{xT}$ , which is  $e_x/DPI_{out}$ , by replacing  $e_s$  by its internal impedance as shown in Figure 24.

Figure 24. Solving for Current  $i_x(e_x)$

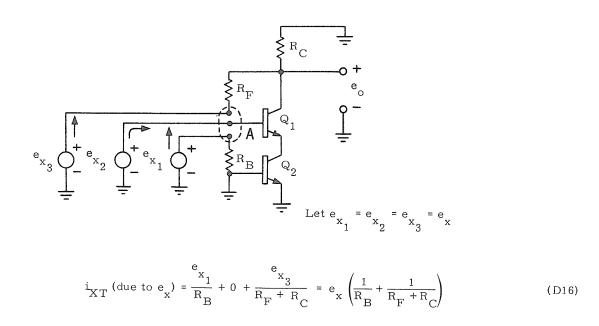

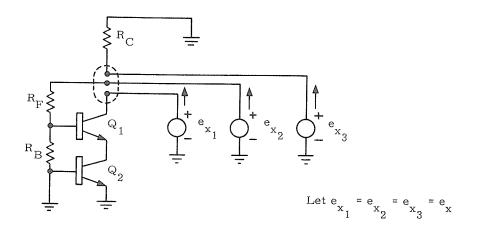

In order to obtain the solution for the  $i_{_{\rm X}}$  current, we apply an external generator to each circuit element connected to the  $e_{_{\rm O}}$  node as shown in Figure 25.

Figure 25. Solving for  $i_{x}(e_{x})$  by Using Multiple External Sources

Once expressions for  $i_x$ ,  $i_x$ , and  $i_x$  have been found by using the superposition theorem,  $e_x$ ,  $e_x$  and  $e_x$  can be set equal to  $e_x$ , and then the sum of  $i_x$ ,  $i_x$ , and  $i_x$  will yield  $i_x$  ( $e_x$ ). Using functional notation, the expression for  $i_x$  ( $e_x$ ) is given by Equation (78).

$$\underbrace{\begin{array}{c}

\text{Currents caused by e} \\

\text{source = i} \\

\text{x}_{1}

\end{array}}_{\text{X}_{1}}$$

$$\underbrace{\begin{array}{c}

\text{Currents caused by e} \\

\text{source = i} \\

\text{x}_{1}

\end{array}}_{\text{X}_{1}}$$

$$\underbrace{\begin{array}{c}

\text{Currents caused by e} \\

\text{source = i} \\

\text{x}_{2}

\end{array}}_{\text{X}_{2}}$$

$$\underbrace{\begin{array}{c}

\text{Currents caused by e} \\

\text{source = i} \\

\text{x}_{2}

\end{array}}_{\text{X}_{3}}$$

$$\underbrace{\begin{array}{c}

\text{Currents caused by e} \\

\text{source = i} \\

\text{x}_{3}

\end{array}}_{\text{X}_{3}}$$

$$\underbrace{\begin{array}{c}

\text{Currents caused by e} \\

\text{source = i} \\

\text{x}_{3}

\end{array}}_{\text{X}_{3}}$$

Inspection of Figure 25 will show that many of the terms of Equation (78) are equal to zero, namely,  $i \times_2 (e \times_1)$ ,  $i \times_3 (e \times_1)$ ,  $i \times_1 (e \times_2)$  and  $i \times_1 (e \times_3)$ .

Solving for i, i, and i by superposition to find i, we have

$$\mathbf{i_{x}} = \frac{\mathbf{e_{x_{1}}}}{\mathbf{R_{L}}} + 0 + 0 + 0 + 0 + \left( \frac{\mathbf{e_{x_{2}}}}{\mathbf{R_{2}} + \left\{ \mathbf{R_{3}} \right\| \left( \mathbf{R_{1}} + \left[ \mathbf{R_{4}} \right\| \mathbf{R_{5}} \right] \right\} \right)} \right) \left( 1 - \left\{ \frac{\mathbf{R_{3}}}{\mathbf{R_{3}} + \left\{ \mathbf{R_{1}} + \left( \mathbf{R_{4}} \right\| \mathbf{R_{5}} \right) \right\} \right\} \\ = \left\{ \frac{\mathbf{R_{5}}}{\mathbf{R_{4}} + \mathbf{R_{5}}} \right\} + \left( \frac{\mathbf{R_{5}}}{\mathbf{R_{4}} + \mathbf{R_{5}}} \right) + \left( \frac{\mathbf{R_{5}}}{\mathbf{R_{4}} + \mathbf{R_{5}}} \right) + \left( \frac{\mathbf{R_{5}}}{\mathbf{R_{4}} + \mathbf{R_{5}}} \right) \right) \\ = \left( \frac{\mathbf{R_{5}}}{\mathbf{R_{4}} + \mathbf{R_{5}}} \right) + \left( \frac{\mathbf{R_{5}}}{\mathbf{R_{5}} + \left\{ \mathbf{R_{5}} \right\} + \left\{ \mathbf{R_{$$

$$0 + \left(\frac{e_{x_{3}}}{R_{4} + \left(R_{5} \| \left\{R_{1} + \left(R_{2} \| R_{3}\right)\right\}\right)} - \left(1 - \left\{\frac{R_{5}}{R_{5} + \left\{R_{1} + \left(R_{2} \| R_{3}\right)\right\}\right\}} - \left\{\frac{R_{3}}{R_{3} + R_{2}}\right\}\right) \right)$$

$$(79)$$

Now, setting  $e_{x_1} = e_{x_2} = e_{x_3} = e_{x_3}$  and getting Equation (79) in the form  $i_x(e_x) = \frac{e_x}{DPI_0}$ , we have the portion of  $i_{xT}$  (Figure 24) caused by the  $e_x$  source.

$$i_{x} = e_{x} \left\{ \frac{1}{R_{L}} + \frac{1}{\left\{ \frac{R_{2} + \left\{ R_{3} \| \left( R_{1} + \left[ R_{4} \| R_{5} \right] \right) \right\}}{R_{3} + \left[ \frac{R_{3} + \left[ R_{1} + \left( R_{4} \| R_{5} \right] \right] \right\}}{R_{4} + R_{5}}} \right\}} + \frac{1}{\left\{ \frac{R_{4} + \left( R_{5} \| \left\{ R_{1} + \left( R_{2} \| R_{3} \right) \right\} \right)}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right] \right\}}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right] \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right] \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right] \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{1} + \left( R_{2} \| R_{3} \right) \right]}{R_{5} + \left[ \frac{R_{5} + \left[ R_{1} + \left( R_{2$$

The expression for the output DPI can be taken from Equation (80) by observing that the terms within the large braces must each have the dimensions of 1/ohms. Recalling that the total impedance of many parallel impedances is given by Equation (81), we can see that the DPI out from Equation (80) is given in Equation (82).

$$\frac{1}{R_{\rm T}} = \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3} = \frac{1}{R_1 \|R_2\| R_3}$$

(81)

$$DPI_{out} = R_{L} \left\{ \frac{R_{2} + \left\{ R_{3} \| \left( R_{1} + \left[ R_{4} \| R_{5} \right] \right) \right\}}{R_{3} + \left[ R_{1} + \left( R_{4} \| R_{5} \right) \right]} \left\{ \frac{R_{5}}{R_{5} + R_{4}} \right\} \right\} \left\{ \frac{R_{4} + \left( R_{5} \| \left\{ R_{1} + \left( R_{2} \| R_{3} \right) \right\} \right)}{R_{5} + \left[ R_{1} + \left( R_{2} \| R_{3} \right) \right]} \left\{ \frac{R_{3}}{R_{3} + R_{2}} \right\} \right\}$$

(82)

Using Equation (76), and substituting into it the expressions for DPI out  $_{out}$  and  $_{osc}$  from Equations (77) and (82), we have the complete expression for  $_{o}$  as a function of  $_{e}$  as shown in Equation (83).

$$\frac{e_{o}}{e_{o}} = \left( \left\{ \frac{e_{s}}{R_{5} + \left[R_{4} \right] \left\{R_{1} + \left[R_{2} \right] R_{3}\right\}} \right) \left\{ \left( \frac{R_{1} + \left[R_{2} \right] R_{3}}{R_{1} + \left[R_{2} \right] R_{3}\right] + R_{4}} \right) + \left( \frac{R_{4}}{R_{4} + R_{1} + \left[R_{2} \right] R_{3}} \right) \left( \frac{R_{3}}{R_{3} + R_{2}} \right) \right\} \right) \cdot \left( \frac{e_{s}}{R_{5} + \left[R_{4} \right] \left\{R_{1} + \left[R_{4} \right] R_{5}\right\}} \right) \left\{ \frac{e_{s}}{R_{5} + R_{4}} \right\} \left\{ \frac{R_{4} + \left(R_{5} \right) \left\{R_{1} + \left(R_{2} \right) R_{3}\right\}\right\}}{R_{5} + \left[R_{1} + \left(R_{2} \right] R_{3}\right]} \right\} \left\{ \frac{R_{3}}{R_{3} + R_{2}} \right\} \right\} \right) \cdot \left( \frac{R_{4} + \left(R_{5} \right) \left\{R_{1} + \left(R_{2} \right) R_{3}\right\}\right\}}{R_{5} + \left[R_{1} + \left(R_{2} \right) R_{3}\right]} \right) \left( \frac{R_{3}}{R_{3} + R_{2}} \right) \right) \cdot \left( \frac{R_{3}}{R_{3} + \left[R_{1} + \left(R_{4} \right] R_{5}\right]\right) \left\{ \frac{R_{3}}{R_{5} + R_{4}} \right\} \left( \frac{R_{4} + \left(R_{5} \right) \left\{R_{1} + \left(R_{2} \right) R_{3}\right\}\right)}{R_{3} + R_{2}} \right) \right) \cdot \left( \frac{R_{3}}{R_{3} + R_{2}} \right) \right) \left( \frac{R_{3}}{R_{3} + R_{2}} \right) \left( \frac{R_{3}}{$$

At this point it is probably not at all evident that the use of DPI analysis to obtain Equation (83) has any advantage over loop or node analysis. In reality, it would be ridiculous to solve this circuit (Figure 19) by DPI analysis; the actual value of this approach will not be evident unitl feedback circuits are investigated.

## Application of DPI Analysis to a Feedback Amplifier

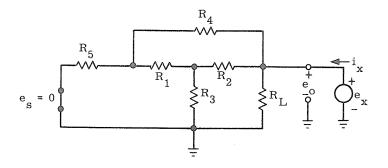

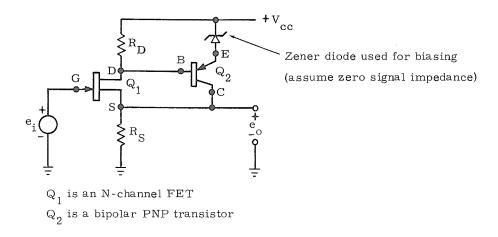

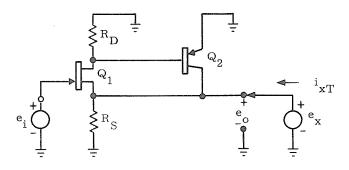

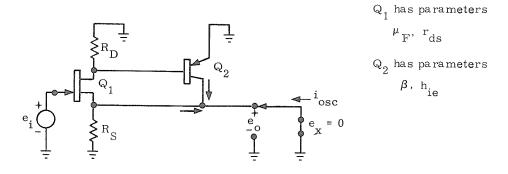

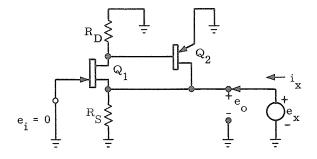

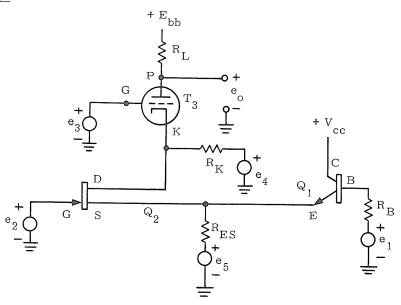

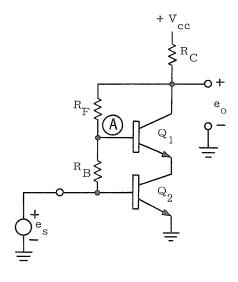

The feedback amplifier of Figure 26 will be analyzed using DPI analysis and the technique presented for handling nonseries parallel circuits.

Figure 26. Amplifier Circuit Containing Feedback

The circuit of Figure 26 is classified as a feedback circuit because a portion of the output current is fed back to the input in such a way as to modify the conditions existing in the input circuitry. In this case, the collector current of  $\mathbf{Q}_2$  modifies the source current of  $\mathbf{Q}_1$ . Assume for the moment that the output impedance of this amplifier is needed. The inexperienced user of DPI analysis would look into the output terminal and say that the output DPI is just  $\mathbf{R}_s$  in parallel

with the source DPI of the FET  $\mathbf{Q}_1$ . This answer will be shown to be incorrect because the feedback causes the output impedance to be modified. The DPI equations needed for the analysis of this circuit are repeated here for convenience.

$$\begin{bmatrix} i_{d} = i_{S} = \left(\frac{\mu_{F} e_{i}}{r_{dS} + R_{D} + (1 + \mu_{F})R_{S}}\right) \\ Source DPI = \left(\frac{r_{dS} + R_{D}}{(1 + \mu_{F})}\right) \\ Drain DPI = r_{dS} + (1 + \mu_{F})R_{S} \\ Gate DPI = \infty \end{bmatrix}$$

$$\begin{bmatrix} Collector DPI = \infty \\ Base DPI = h_{ie} + (1 + \beta)R_{e} \\ Emitter DPI = \left(\frac{h_{ie} + R_{B}}{1 + \beta}\right) \end{bmatrix}$$

$$Emitter DPI = \left(\frac{h_{ie} + R_{B}}{1 + \beta}\right)$$

$$Bipolar$$

$$Transiston$$

The amplifier voltage gain  $\frac{e_0}{e_i}$  and output DPI will be found using the signal circuit shown in Figure 27.

Figure 27. Signal Circuit of Feedback Amplifier

The external source  $e_x$  is applied to the output terminal <u>in order to disable feedback</u> and permit easy analysis of the circuit by conventional DPI methods. The  $i_{xT}$  current is a function of  $e_i$  and  $e_v$  as indicated in Equation (84).

$$i_{xT} = f(e_x, e_i)$$

(84)

By applying the superposition theorem, we know that

$$i_{xT} = i_{x} (e_{x} = 0, e_{i}) + i_{x} (e_{x}, e_{i} = 0)$$

(85)

and observation will show that

$$i_{x}(e_{x} = 0, e_{i}) = i_{osc}$$

(output short circuit current) (86)

$$i_x (e_x, e_i = 0) = \frac{e_x}{DPI}$$

(output DPI) (87)

So

$$i_{xT} = i_{osc} + \frac{e_x}{DPI_o}$$

(88)

If we adjust the ficticious  $e_{x}$  generator so that it is equal to  $e_{o}$ , then  $i_{xT} = 0$  and Equation (88) becomes

$$0 = i_{\text{osc}} + \frac{e_{\text{o}}}{\text{DPI}_{\text{o}}}$$

(89)

Solving for e, we finally get

$$e_{o} = -i_{osc} DPI_{o}$$

(90)

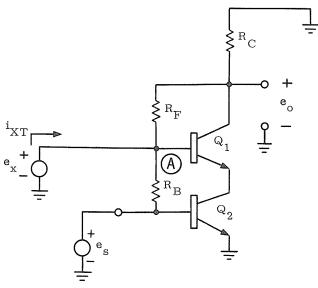

In solving for the current  $i_{\rm xT}$  of Equation (85), we obtain both an expression for  $e_{\rm o}$  and the output DPI. First,  $i_{\rm osc}$  will be found. The circuit of Figure 27 has been redrawn in Figure 28 to clarify the procedure.

Figure 28. Solving for  $i_{\text{osc}}$  in the Feedback Amplifier

$$i_{osc} = -\left(\frac{\mu_{F}e_{i}}{r_{ds} + (R_{D} || h_{ie})}\right) \left[ 1 + \left(\frac{R_{D}}{R_{D} + h_{ie}}\right)\beta \right]$$

Expression for source and drain current of  $Q_{1}$

equal to the source caused by source current of  $Q_{2}$  collector of  $Q_{1}$

equal to the source of  $Q_{1}$

equal to the source of  $Q_{2}$  collector current of  $Q_{3}$

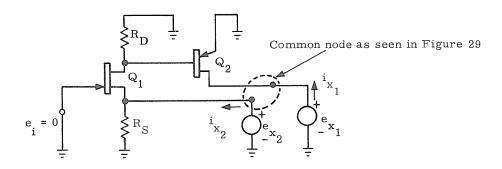

Second, the portion of the  $i_{xT}$  current caused by the  $e_x$  generator will be determined. The circuit of Figure 27 has been redrawn in Figures 29 and 30 to clarify the procedure.

Figure 29. Solving for the Current i

Figure 30. Solving for Current  $i_x$  by Splitting the  $e_x$  Source

$$i_x(e_x) = i_{x_1} + i_{x_2}$$

when  $e_{x_1} = e_{x_2} = e_x$

The current  $i_x(e_x)$  is more easily determined by splitting the  $e_x$  generator and using superposition as shown in Figure 30. The total  $i_x(e_x)$  current is found by setting  $e_x = e_x$  and summing the individual currents.

$$i_{x} = \left(\frac{e_{x}}{R_{S} \left\| \left\{ \frac{r_{ds} + (R_{D} \| h_{ie})}{1 + \mu_{F}} \right\} \right) \left[ 1 + \left( \frac{R_{S}}{R_{S} + \left\{ \frac{r_{ds} + (R_{D} \| h_{ie})}{1 + \mu_{F}} \right\} \right) \left( \frac{R_{D}}{R_{D} + h_{ie}} \right) \beta \right] + 0$$

(92)

Observe that we previously determined that  $i_x = \frac{e_x}{DPI_o}$  so that we can now write DPI from inspection of Equation (92).

$$DPI_{o} = \left\{ \frac{R_{S} \left\| \left\{ \frac{r_{ds} + (R_{D} \|^{h}_{ie})}{1 + \mu_{F}} \right\} - \left( \frac{R_{S}}{1 + \mu_{F}} \right\} - \left( \frac{R_{D}}{1 + \mu_{F}} \right) \right\} - \left( \frac{R_{D}}{R_{D} + h_{ie}} \right) \beta \right\}$$

$$(93)$$

Recall that in the beginning of this problem, the statement was made that the output DPI was not the parallel combination of  $R_S$  and the DPI of the  $Q_1$  source. Equation (93) shows that the output DPI of the amplifier has been reduced due to the feedback, thus confirming the statement.

Using Equation (90) we can now write the complete expression for e

$$e_{o} = -i_{osc} DPI_{o}$$

$$e_{o} = \left(\frac{\mu_{F}e_{i}}{r_{ds} + (R_{D} \| h_{ie})}\right) \left[1 + \left(\frac{R_{D}}{R_{D} + h_{ie}}\right)\beta\right] \left\{\frac{R_{S} \|\left(\frac{r_{ds} + (R_{D} \| h_{ie})}{1 + \mu_{F}}\right)}{1 + \left(\frac{R_{D} \| h_{ie}}{1 + \mu_{F}}\right)\left(\frac{R_{D}}{R_{D} + h_{ie}}\right)\beta}\right\}$$

$$OPI_{o}$$

$$OPI_{o}$$

$$OPI_{o}$$

Dividing both sides of Equation (94) by  $e_i$  yields the desired expression for voltage gain.

If the ideal FET equations (Equations 52A, 53, 54A, 55A) had been used, Equation (94A) would have resulted. Equation (94A) can be obtained by taking the limit as  $r_{ds} \rightarrow \infty$  of Equation (94). Of course, it would be easier to use the ideal FET equations in the first place.

$$e_{o} = \left(\frac{e_{i}}{\frac{1}{g_{m}}}\right) \left[1 + \left(\frac{R_{D}}{R_{D} + h_{ie}}\right)\beta\right] \left\{\frac{R_{S} \left\|\left\{\frac{1}{g_{m}}\right\}\right\}}{1 + \left(\frac{R_{S}}{R_{S} + \frac{1}{g_{m}}}\right) \left(\frac{R_{D}}{R_{D} + h_{ie}}\right)\beta}\right\}$$

$$\stackrel{-i_{osc}}{= osc} \qquad DPI_{O}$$

As pointed out in previous examples, an explanation of the reasoning process behind the analysis procedure is far more tedious than the procedure itself. A single example is certainly not sufficient to explain all of the subtleties of applying DPI analysis to the solution of feedback circuits, but it does make the reader aware of some of the pitfalls, and this was its purpose.

In order to gain a more thorough insight into the application of DPI analysis, the example problems in Appendix D should be worked and References 6, 7, and 8 should be studied.

## APPENDIX A

## REVIEW OF THEVENIN'S AND NORTON'S THEOREMS

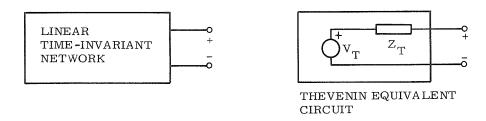

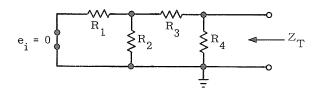

## Thevenin's Theorem

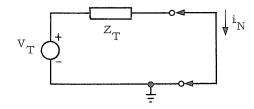

The venin's theorem  $^4$  states that any linear time-invariant oneport network can be replaced by a single voltage source  $V_T$  in series with an impedance  $Z_T$ , and as far as the external terminal conditions are concerned, the Thevenin equivalent circuit cannot be distinguished from the original if  $V_T$  and  $Z_T$  have been properly chosen. This is shown in Figure A1.

Figure A1. Application of Thevenin's Theorem

A simple procedure for determining the Thevenin equivalent circuit of a linear time-invariant oneport network follows:

- 1. Remove any networks connnected to the oneport.

- 2. Determine the voltage appearing at the terminals of the oneport by any convenient analysis or measurement technique. This voltage is referred to as the open-circuit or Thevenin voltage  $\mathbf{V}_{\mathbf{T}}$ .

- 3. Replace all independent voltage and current sources by their internal impedances and determine the impedance seen looking into the terminals of the oneport by any convenient analysis or measurement technique. This impedance is referred to as the Thevenin equivalent impedance.

- 4. Replace the original linear time-invariant oneport with its Thevenin equivalent circuit.

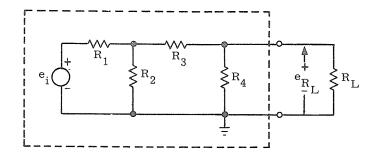

## Example A1

Determine the Thevenin equivalent circuit of the oneport shown within the dotted lines (Figure A2). Using both the original network and its Thevenin equivalent, determine the voltage across the load resistor  $\mathbf{R}_{\mathsf{T}}$  and show that both expressions are the same.

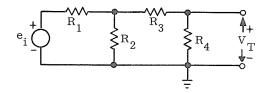

Figure A2. Network Under Consideration

The Thevenin voltage  $\mathbf{V}_T$  is found by removing  $\mathbf{R}_L$  and computing the voltage appearing across the open circuited terminals as shown in Figure A3.

Figure A3. Determination of Thevenin Voltage  $V_{\mathrm{T}}$

$$V_{T} = e_{i} \left[ \frac{R_{2} \parallel (R_{3} + R_{4})}{\left\{ R_{2} \parallel (R_{3} + R_{4}) \right\} + R_{1}} \right] \left[ \frac{R_{4}}{R_{4} + R_{3}} \right]$$

Portion of  $e_{i}$  appearing across  $R_{2}$  which appears across  $R_{4}$

Voltage divider fractions were used to write Equation (A1) by inspection. This technique is explained in the main body of the report. Any other convenient technique can be applied, but this one is probably the simplest to use.

The Thevenin impedance  $\mathbf{Z}_{T}$  is found by removing  $\mathbf{R}_{L}$  and replacing all independent sources by their internal impedances as shown in Figure A4.

Figure A4. Determination of Thevenin Impedance

$$Z_{T} = \left\{ R_{4 \parallel} \left( R_{3} + \left[ R_{1} + R_{2} \right] \right) \right\} \tag{A2}$$

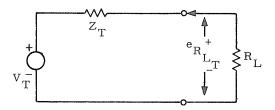

The complete Thevenin equivalent circuit with the load  $\boldsymbol{R}_{_{\boldsymbol{T}}}$  connected is shown in Figure A5.

Figure A5. Thevenin Equivalent Circuit of Oneport Shown in Figure A3

Solving for the voltage e  ${\rm R}_{\rm L}$  across  ${\rm R}_{\rm L}$  using the Thevenin equivalent circuit of Figure A5, we have Equation (A3).

$$e_{R_{L_{T}}} = V_{T} \left[ \frac{R_{L}}{R_{L} + Z_{T}} \right] \tag{A3}$$

Substituting the expressions found for  $V_T$  and  $Z_T$  (Equations A1 and A2) into Equation (A3), we have Equation (A4).

$$e_{R_{L_{T}}} = e_{i} \left[ \frac{R_{2} \| (R_{3} + R_{4})}{R_{2} \| (R_{3} + R_{4}) + R_{1}} \right] \left[ \frac{R_{4}}{R_{3} + R_{4}} \right] \left[ \frac{R_{L}}{R_{L} + \left[ R_{4} \| (R_{3} + |R_{1}| R_{2}) \right]} \right]$$

(A4)

Now, using Figure A2, an expression for  $e_{R_{\tau}}$  will be written directly.

$$e_{R_{L}} = e_{i} \left[ \frac{\left\{ R_{2} \| \left[ R_{3} + (R_{4} \| R_{L}) \right] \right\}}{\left\{ R_{2} \| \left[ R_{3} + (R_{4} \| R_{L}) \right] \right\} + R_{1}} \right] \left[ \frac{\left( R_{4} \| R_{L} \right)}{\left( R_{4} \| R_{L} \right) + R_{3}} \right]$$

(A5)

After simplification, Equations (A4) and (A5) can be shown to be identical, indicating that the Thevenin equivalent circuit has the same terminal characteristics as the original circuit. Another way to check and see if Equations (A4) and (A5) produce the same answer is to choose some convenient values for the circuit components and sources. If all R's are chosen to be  $1\Omega$  and e and e and e will be found to be 1 volt.

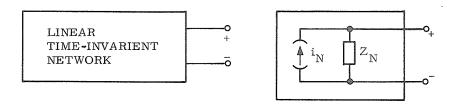

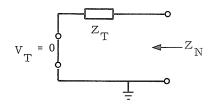

## Norton's Theorem

Norton's theorem<sup>5</sup> is the dual of Thevenin's theorem, and states that any linear time-invariant oneport network can be replaced by a single current source  $i_N$  in shunt with an impedance  $Z_N$ , and as far as the external terminal conditions are concerned, the Norton equivalent circuit cannot be distinguished from the original oneport if  $i_N$  and  $Z_N$  are chosen properly. This is shown in Figure A6.

Figure A6. Application of Norton's Theorem

A simple procedure for determining the Norton equivalent circuit of a linear time-invariant oneport follows:

- 1. Remove any networks connected to the oneport.

- 2. Short the terminals of the oneport and determine the short-circuit current that flows by any convenient analysis or measurement technique. This current is referred to as the Norton current  $i_{N^{\bullet}}$

- 3. Replace all independent sources by their internal impedances and determine the impedance seen looking into the terminals of the oneport by any convenient analysis or measurement technique. This impedance is referred as the Norton impedance  $\mathbf{Z}_{N}$ .

- 4. Replace the original linear time-invariant oneport with its Norton equivalent circuit.

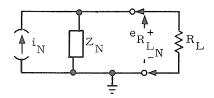

#### Example A2

Using the Thevenin equivalent circuit found in Example A1 (Figure A5), determine its Norton equivalent circuit and then solve for e  $_{\rm R}$  using the Norton equivalent circuit and show that the answer is the same as given by Equation (A4).

The Norton current  $i_{\rm N}$  is found by removing  $R_{\rm L}$  and computing the current flowing through the short as shown in Figure A7.

Figure A7. Determination of Norton Current

$$i_{N} = \frac{V_{T}}{Z_{T}}$$

(A6)

The Norton impedance  $\mathbf{Z}_{N}$  is found by removing  $\mathbf{R}_{L}$ , replacing  $\mathbf{V}_{T}$  by its internal impedance (short circuit), and measuring the impedance seen looking into the oneport terminals as shown in Figure A8.

Figure A8. Determination of Norton Impedance

$$Z_{N} = Z_{T}$$

The complete Norton equivalent circuit is shown in Figure A9 with the load connected.

Figure A9. Norton Equivalent Circuit of Figure A5

$$e_{R_{L_{N}}} = i_{N} \left( \frac{Z_{N}}{Z_{N} + R_{L}} \right) R_{L} \tag{A7}$$

$$e_{R_{L_{N}}} = \frac{v_{T}}{Z_{T}} \left(\frac{z_{T}}{z_{T} + R_{L}}\right) R_{L} = v_{T} \left(\frac{R_{L}}{z_{T} + R_{L}}\right)$$

(A8)